#### 3D TECHNOLOGIES: SEVERAL DISRUPTIVE TECHNOLOGIES TO LOOK AHEAD

- Top Challenges for Computing

- 2 How 3D Can Help?

- **3** Our Options Towards Fine Pitch

- 4 Summary

#### Leti CE2 LECH TOP CHALLENGES FOR COMPUTING

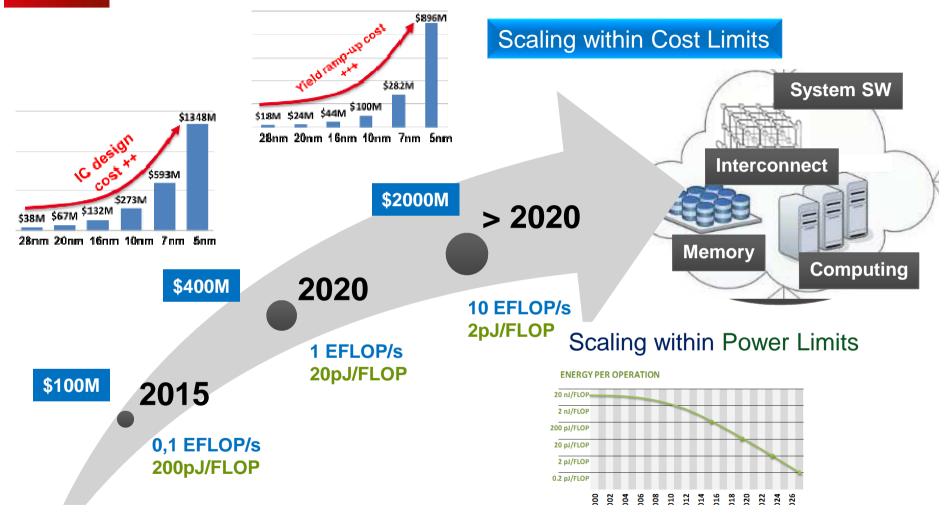

- 1. <u>Cost</u>: Disruptive Architecture and Integration Technologies are Required

- 2. <u>Performance</u>: Disruptive Technologies are Required

- Quantum Computing

- Neuromorphic Architectures

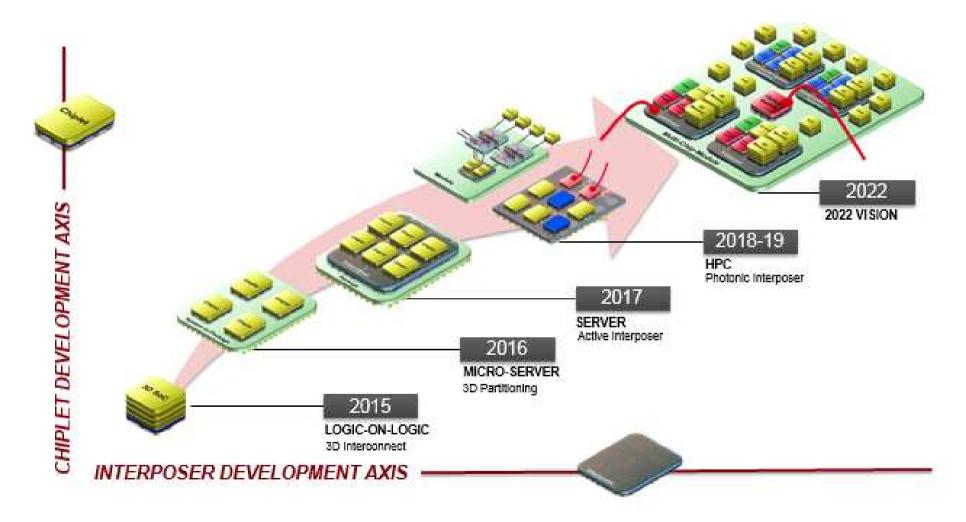

#### 2020 Technological Shift

- New Memory Materials and Architecture

- 3D VLSI and High-Density 3D

- Integrated Silicon Photonic Dies

- Neuromorphic for Advanced Chiplet Architecture

# **2015**

#### **Integration Shift**

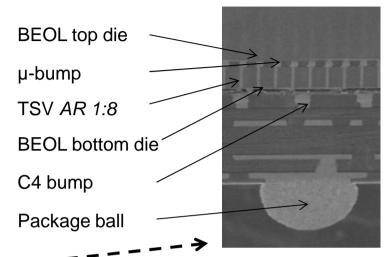

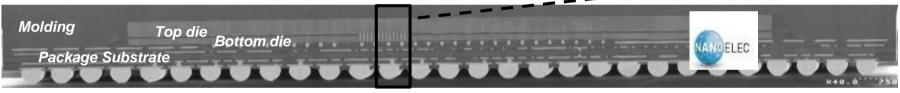

- **3D Integrated Circuits**

- Interposer Integrated Chiplets

- Integrated Photonic Links

[1] Cheramy, S., et al. "Advanced Silicon Interposer", C2MI Workshop, 2015

[2] Patti, B., "Implementing 2.5D and 3D Devices", In AIDA workshop in Roma, 2013

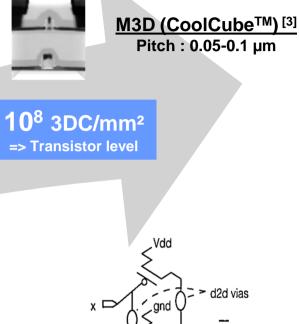

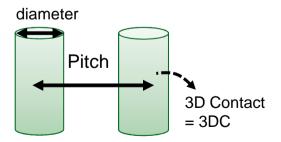

[3] Batude, P., et al. "3DVLSI with CoolCube process: An alternative path to scaling ." VLSI technology symposium 2015

[1] Cheramy, S., et al. "Advanced Silicon Interposer", C2MI Workshop, 2015

[2] Patti, B., "Implementing 2.5D and 3D Devices", In AIDA workshop in Roma, 2013

[3] Batude, P., et al. "3DVLSI with CoolCube process: An alternative path to scaling ." VLSI technology symposium 2015

## **HOW 3D CAN HELP?**

#### **Network-on-Chip 3D Asynchron**

- Multi core aplications, high bandwidth

- Serial links

- Logic on Logic stack

- Fauls tolerance, repair

|                            | GeorgiaTech<br>ISSCC'2012 | Kobe Univ.<br>ISSCC'2013        | This Work                        |

|----------------------------|---------------------------|---------------------------------|----------------------------------|

| Architecture               | Cache-on-CPU<br>Manycore  | Memory-on-Logic<br>1 layer DRAM | Logic-on-Logic<br>2 layers 3DNOC |

| Process &<br>3D technology | 130nm<br>F2F CuCu         | 90nm<br>F2B TSV                 | 65nm<br>F2B TSV                  |

| 3D Bandwidth               | 277 Mbps                  | 200 Mbps                        | 326 Mbps                         |

| 3D I/O Power               | -                         | 0.56 pJ/bit                     | 0.32 pJ/bit                      |

|                            |                           |                                 |                                  |

[P. Vivet et al. ISSCC'16]

### **3D Link Performances**

- Fastest Link, +20% (326 Mflit/s)

- Best Energy Efficiency, +40% (0.32 pJ/bit)

- Self-Adaptation to Temperature, a Strong 3D Concern

[1] Cheramy, S., et al. "Advanced Silicon Interposer", C2MI Workshop, 2015

[2] Patti, B., "Implementing 2.5D and 3D Devices", In AIDA workshop in Roma, 2013

[3] Batude, P., et al. "3DVLSI with CoolCube process: An alternative path to scaling ." VLSI technology symposium 2015

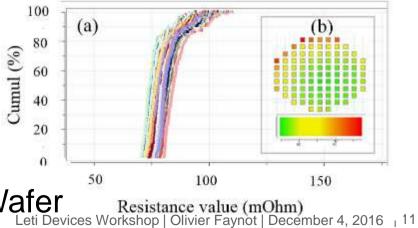

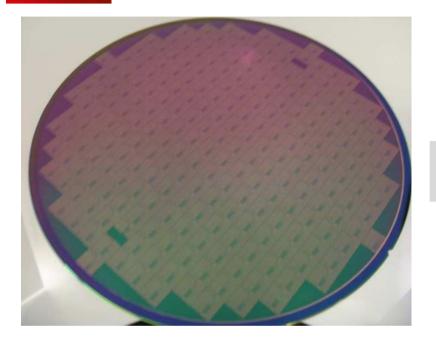

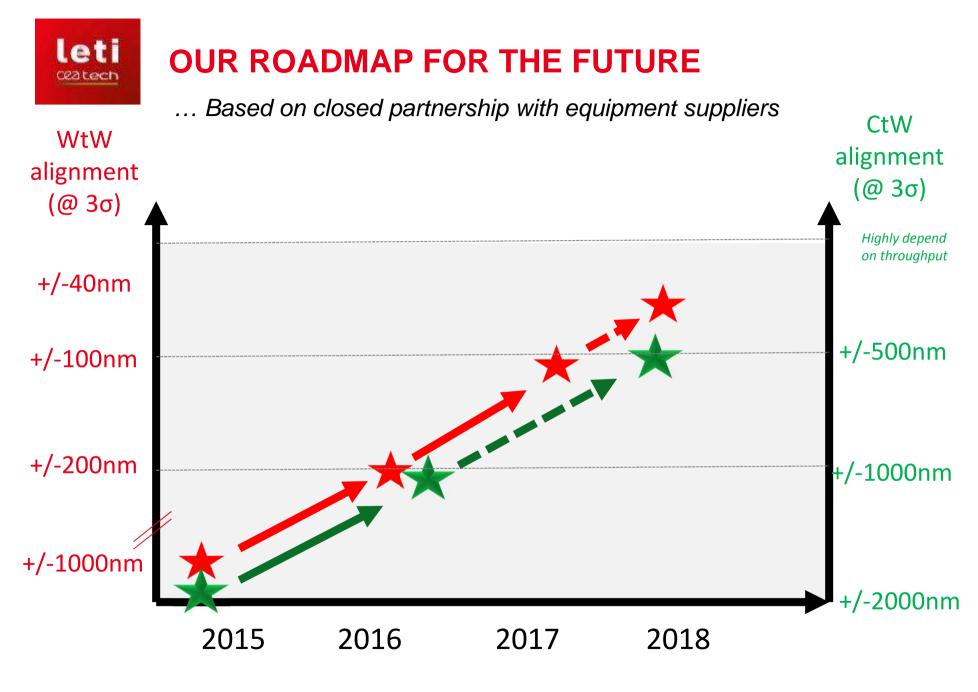

### WAFER TO WAFER OR CHIP TO WAFER?

#### Wafer-to-wafer

Objectives:

- Ultra Fine Pitch

- Throughput

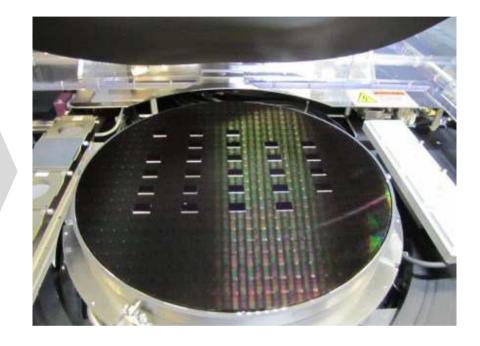

#### Chip-to-wafer

Objectives:

- Heterogeneity

- Multi Dies Stacking

- Low Yield Devices Stacking

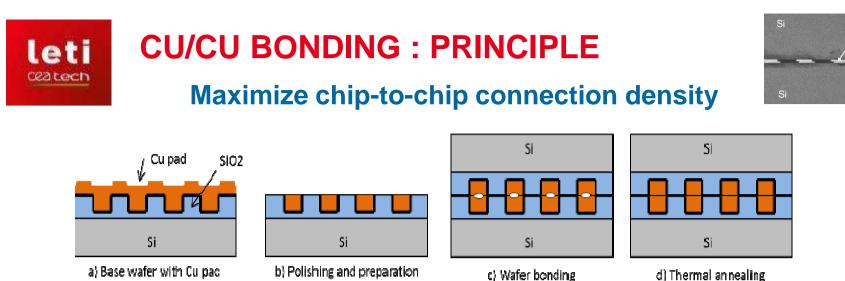

- No adhesive (underfill), No pressure, Room T° process: high throughput

- ✓ From 200°C to 400°C annealing

- ✓ Pitch : 5-10µm (2015) => 1-2µm (2017)

L. Benaissa et al, EPTC 2015 Lacourbe S.et al,, ECT2016

Demonstration done on Wafer to Wafer

### WAFER TO WAFER OR CHIP TO WAFER?

#### Wafer-to-wafer

Objectives:

- Ultra Fine Pitch

- Throughput

#### Chip-to-wafer

Objectives:

- Heterogeneity

- Multi Dies Stacking

- Low Yield Devices Stacking

### **CHIP-TO-WAFER INTEGRATION PROCESS**

**BEST ALIGNMENT : 200nm** FC300 bonding machine with ± 0.5µm post-bonding accuracy set X misalignment (µm) 1,5 -2 -1.5 1,5 -1.5 1,5 Y misalignment (µm) .2

## **SELF-ASSEMBLY FOR CHIP TO WAFER APPROACH**

#### PRINCIPLE OF SELF-ASSEMBLY USING CAPILLARY FORCE

Phase 2 : Hybridation Phase 1 : Self-Alignment Leti's choice: capillary driven alignment Leti's choice : Direct bonding Minimization of surface tension with capillary force  $\geq$ 1 - LIQUID DEPOSITION ON SUBSTRATE OR DIE 5 1 2 – ROUGH PRE-POSITIONNING **USING MECHANICAL TOOL** 3 – REMOVAL OF THE TOP DIE 2) (4) **4 – SPONTANEOUS ALIGNMENT** THANKS TO CAPILLARY FORCE (3) **5 – LIQUID EVAPORATION AND HYBRIDATION** S. Mermoz, EPTC 2013 High Throughput **Collective Bonding** High Alignment Accuracy (< 1  $\mu$ m) **Direct Bonding Compatibility** | 14

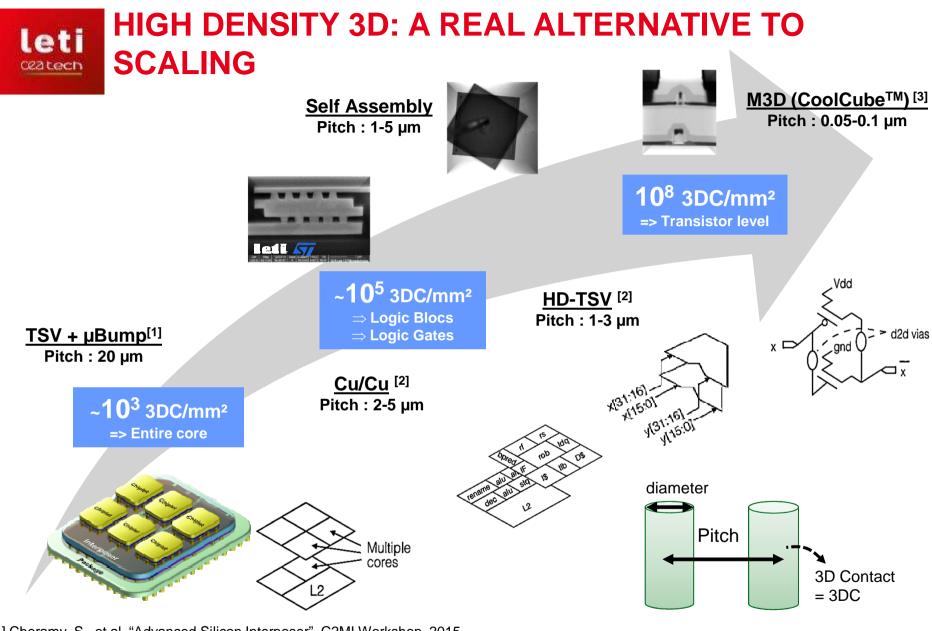

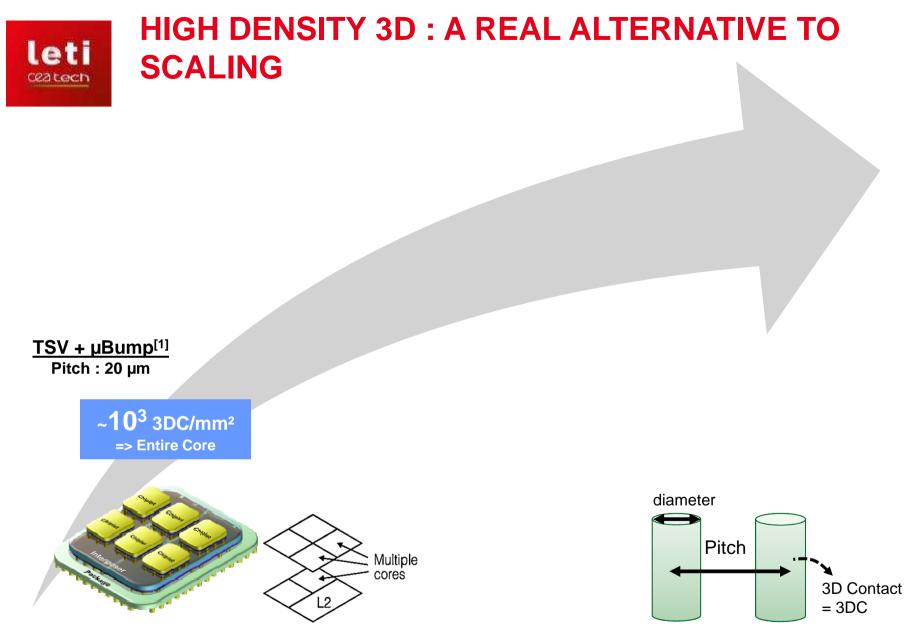

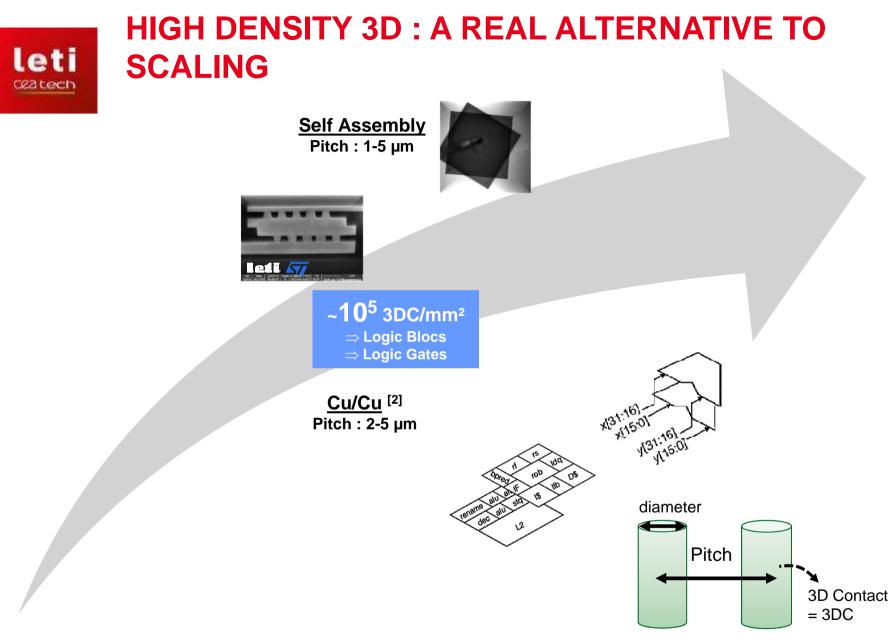

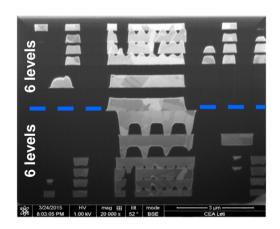

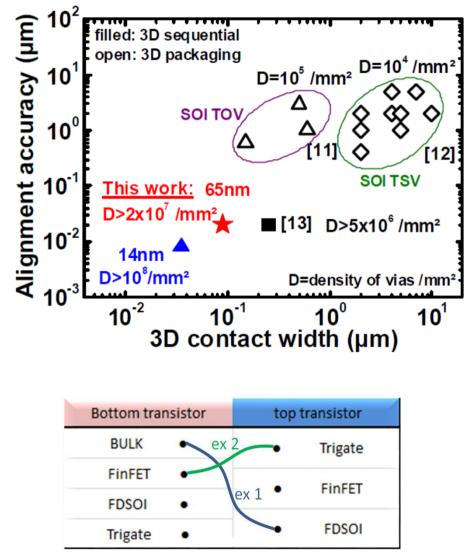

#### HIGH DENSITY 3D : A REAL ALTERNATIVE TO SCALING

[1] Cheramy, S., et al. "Advanced Silicon Interposer", C2MI Workshop, 2015

leti

Ceatech

[2] Patti, B., "Implementing 2.5D and 3D Devices", In AIDA workshop in Roma, 2013

[3] Batude, P., et al. "3DVLSI with CoolCube process: An alternative path to scaling ." VLSI technology symposium 2015

- Yes, 3D Can Help the Computing Roadmap!

- Early Demonstrations Done!

- LETI is Working Towards Several Disruptive Options Devoted to Fine Alignement and Fine Pitches

- Cu/Cu Hybrid Bonding to Achieve 1µm Pitch on Wafer to Wafer Approaches

- Self-Assembly for Die to Wafer and high Troughputs

- Coolcube<sup>TM</sup> Technology for Transistor Level Connections

Part of this work was partly funded thanks to the French national program "Programme d'Investissements d'Avenir, IRT Nanoelec" ANR-10-AIRT-05.

# Thank you for your attention

Leti, technology research institute Commissariat à l'énergie atomique et aux énergies alternatives Minatec Campus | 17 rue des Martyrs | 38054 Grenoble Cedex | France www.leti.fr